画像信号処理IP※1「IPSILOS※2」を開発

~さまざまな市場から要求される高画質映像を実現する技術として他社へのIP提供も想定~

株式会社JVCケンウッドは、映像関連機器の高画質化を実現する画像信号処理IP「IPSILOS(イプシロス)」を新たに開発しましたので、お知らせいたします。このたび開発した「IPSILOS」は、当社製の民生用/業務用ビデオカメラで使用してきた画像信号処理SoC※3「FALCONBRID(ファルコンブリッド)」をベースに基本性能を強化・拡張しており、車載向けを始めさまざまな用途における映像関連機器の高画質化を実現する技術として当社機器に搭載するほか、社外への幅広い提供を想定しています。

※3:System-on-a-chipの略

<企画背景>

近年、スマートフォンに搭載されているカメラの高機能化が加速しており、当社の主力製品の一つであるドライブレコーダーも含めた映像関連機器の“高画質化”に対する市場からの要望は非常に高いものがあります。

このような市場背景において当社は、長年にわたって培ってきた“映像の高画質化”に関する知見やノウハウを生かして、これまで当社製品の高画質性能に寄与してきた独自の画像信号処理SoC「FALCONBRID」をベースに、基本性能の強化・拡張と車載用途にも応用展開が可能となるよう改良を重ねた画像信号処理IP「IPSILOS」を新たに開発しました。「IPSILOS」については当社が展開するさまざまな映像関連機器へ搭載するだけでなく、映像関連機器の高画質化を実現する技術として、スマートフォンを始めとするさまざまな市場で使用されている信号処理SoCを開発するメーカーなどへIPとして提供することも想定しています。今後はこの「IPSILOS」の開発を皮切りに、当社が保有する各種画像信号処理IP群についても他社への提供を検討するとともに、SoC開発メーカーとの開発協業により、さらなる高画質化技術の構築を図ってまいります。

<画像信号処理IP「IPSILOS」の概要>

このたび開発した「IPSILOS」は、一般にはISP(Image Signal Processor)と呼ばれる回路ブロックであり、主にセンサーモジュールからのRGB電気信号を受けY/Cビデオ信号に変換処理する信号処理の回路です。「IPSILOS」の当社製品への搭載はもちろん、回路設計データとしてIP提供、あわせて制御ドライバーソフト環境をSDK(Software Development Kit)提供することで、他社へのライセンス供与や開発協業といった幅広い用途での展開を想定しています。

これにより、半導体開発メーカーが「IPSILOS」を活用することで業界トップクラスの高画質映像を実現するSoCを容易に開発することが可能となるだけでなく、そのSoCを供給された商品開発メーカーはSDKを使って映像に関する各種パラメータを設定することにより、短期間で幅広い商品ラインナップの開発が可能となります。

<画像処理IP「IPSILOS」の仕様概要>

対応配列方式 |

単板RGGB Bayer方式 |

|---|---|

最大処理解像度 |

4480x2520@59.94p(16:9) ※水平最大4800画素まで |

内部処理速度 |

内部合成制約400MHz |

最大同時入力 |

FullHD@59.94p x 2ch FullHD@29.97p x 4ch |

最大処理bit数 |

入力 24bit |

出力フォーマット |

YUV 4:2:2 12bit / 10bit / 8bit |

<主な機能>

カメラ信号処理系

- ・階調変換、伸張を行う区分線形処理

- ・G画素相関検出を用いたDe-Bayer処理

- ・動的白傷補正と黒傷補正(同色2連続まで対応)

- ・リニアマトリクス補正および6軸色補正と黄緑色補正

- ・24bit HDRガンマ処理による明るさ制御 (HDR:144dB)

- ・アダマール変換による輝度・色・アパーチャーノイズリダクション

- ・高輝度・低輝度色抑圧処理

- ・レンズ周辺ボケ補正処理

- ・水平・垂直方向の動き検出を用いた3DNR処理

- ・480分割による分散、ヒストグラム、ピーク値算出、出力総和・平均値算出(AE/AWB/AF)

- ・ヒストグラムを用いたソフトに負荷をかけないダイナミックガンマ処理

- ・視覚的にコントラストを上げる画像強調補正処理

レンズ補正系

- ・シェーディング補正(スプライン補間)

- ・歪曲補正(SRAM対応)

- ・倍率色収差補正

動画系補正系

- ・2シャッターによるHDR合成

- ・蛍光灯(室内など)フリッカー補正回路

<回路構成ブロック>

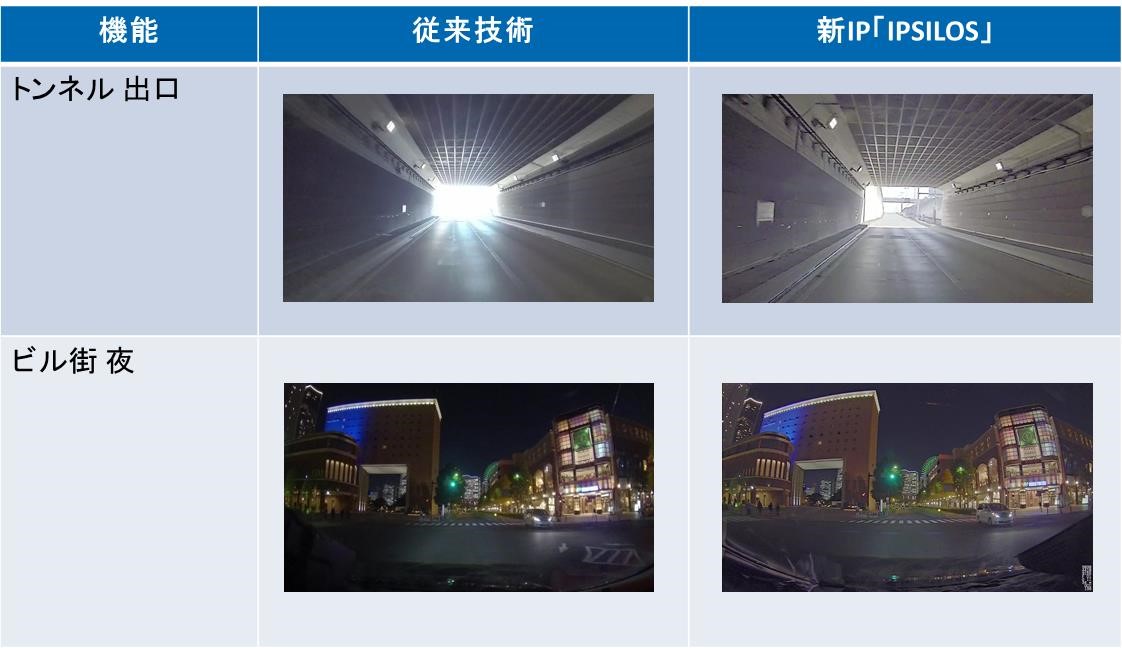

<画質比較>

①HDR(High Dynamic Range)

②画像補正処理

<商標について>

●「IPSILOS」「FALCONBRID」は株式会社JVCケンウッドの商標です。

本件に関するお問い合わせ先

| 【報道関係窓口】 | 株式会社JVCケンウッド 企業コミュニケーション部 広報・IRグループ |

| TEL: 045-444-5232 〒221-0022 神奈川県横浜市神奈川区守屋町3丁目12番地 |

本資料の内容は発表時のものです。最新の情報と異なる場合がありますのでご了承ください。

※1:Intellectual Propertyの略 ※2:Intellectual Property of Special Imaging Logical Optimized Systemの略